1965 елда Intel компаниясенә нигез салучыларның берсе Гордон Мур "Мур законы" дип аталган законны ачыклады. Ярты гасырдан артык вакыт дәвамында ул интеграль микросхемаларның (ИМ) эшләвендә тотрыклы үсеш һәм чыгымнарның кимүенә нигез булды - бу заманча санлы технологияләрнең нигезе иде. Кыскасы: чиптагы транзисторлар саны ике елга якынча ике тапкыр арта.

Еллар дәвамында алгарыш шул темпедансны күзәтеп барды. Хәзер картина үзгәрә. Алга таба кечерәю авырлашты; элементларның зурлыгы берничә нанометрга кадәр генә калды. Инженерлар физик чикләүләр, катлаулырак процесс адымнары һәм артучы чыгымнар белән очрашалар. Кечкенә геометрияләр шулай ук җитештерүчәнлекне киметә, бу зур күләмле җитештерүне катлауландыра. Алдынгы завод төзү һәм эшләтеп җибәрү зур капитал һәм тәҗрибә таләп итә. Шуңа күрә күпләр Мур законының көчен югалта дип саныйлар.

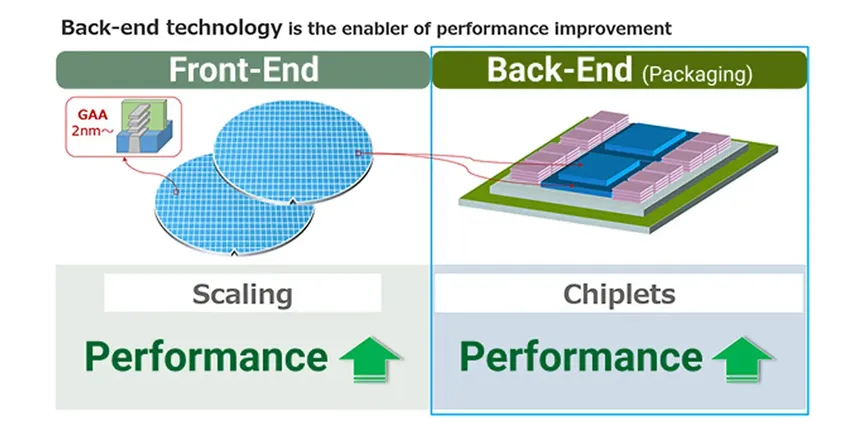

Бу үзгәреш яңа алымга ишек ачты: чиплетлар.

Чиплет - билгеле бер функцияне башкаручы кечкенә штамп - нигездә, элек бер монолит чип булган кисәк. Берничә чиплетны бер пакетка берләштерү аша җитештерүчеләр тулы система җыя алалар.

Монолит чорында барлык функцияләр дә бер зур штампта эшли иде, шуңа күрә теләсә кайсы урында булган җитешсезлек бөтен чипны җимерергә мөмкин иде. Чиплетлар белән системалар "билгеле яхшы штамп"тан (KGD) төзелә, бу җитештерү нәтиҗәлелеген һәм җитештерү нәтиҗәлелеген сизелерлек яхшырта.

Гетероген интеграция - төрле процесс төеннәрендә һәм төрле функцияләр өчен төзелгән штампларны берләштерү - чиплетларны аеруча көчле итә. Югары җитештерүчәнлекле исәпләү блоклары иң яңа төеннәрне куллана ала, ә хәтер һәм аналог схемалар өлгергән, экономияле технологияләрдә кала. Нәтиҗә: түбәнрәк бәядә югарырак җитештерүчәнлек.

Автомобиль сәнәгате аеруча кызыксына. Зур автомобиль җитештерүчеләр бу ысулларны киләчәктәге машина эчендә кулланыла торган SoC'ларны эшләү өчен кулланалар, аларны 2030 елдан соң күпләп куллану планлаштырыла. Чиплетлар аларга ясалма интеллектны һәм графиканы нәтиҗәлерәк масштабларга мөмкинлек бирә, шул ук вакытта җитештерүчәнлекне дә яхшырта - автомобиль ярымүткәргечләрендә җитештерүчәнлекне дә, функциональлекне дә арттыра.

Кайбер автомобиль детальләре катгый функциональ куркынычсызлык стандартларына туры килергә тиеш, шуңа күрә иске, сыналган төеннәргә таянырга тиеш. Шул ук вакытта, алдынгы йөртүче ярдәме (ADAS) һәм программа тәэминаты белән билгеләнгән транспорт чаралары (SDV) кебек заманча системалар күпкә күбрәк исәпләү таләп итә. Чиплетлар бу аерманы бетерә: куркынычсызлык классындагы микроконтроллерларны, зур хәтерне һәм көчле ясалма интеллект тизләткечләрен берләштерү аша җитештерүчеләр SoCларны һәр автомобиль җитештерүченең ихтыяҗларына тизрәк туры китерә ала.

Бу өстенлекләр автомобильләрдән тыш та киңәя. Чиплет архитектуралары ясалма интеллект, телекоммуникация һәм башка өлкәләргә тарала, тармакларда инновацияләрне тизләтә һәм ярымүткәргеч юл картасының терәгенә әйләнә.

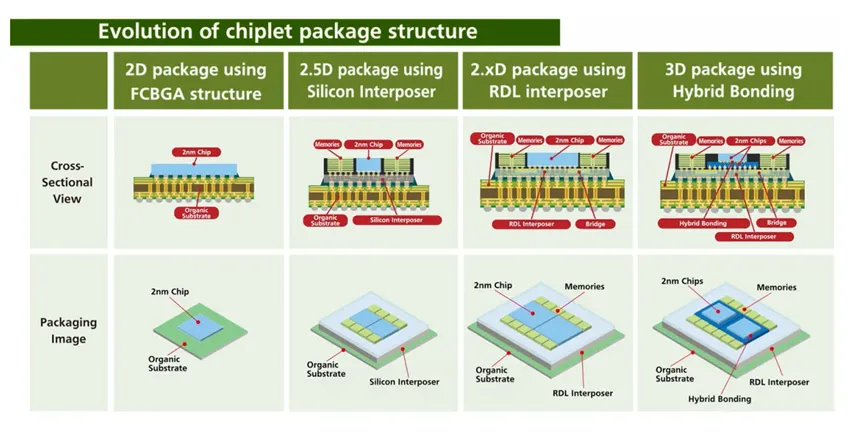

Чиплет интеграциясе компакт, югары тизлекле штамптан штампка тоташуларга бәйле. Төп мөмкинлек бирүче - интерпозер - штамплар астындагы арадаш катлам, еш кына кремний, ул сигналларны кечкенә схема платасы кебек җибәрә. Яхшырак интерпозиторлар тыгызрак тоташу һәм тизрәк сигнал алмашу дигән сүз.

Алдынгы төргәкләү шулай ук электр энергиясен җиткерүне яхшырта. Матрицалар арасындагы кечкенә металл тоташуларның тыгыз массивлары хәтта тар урыннарда да ток һәм мәгълүмат өчен киң юллар тәэмин итә, чикләнгән төргәк мәйданын нәтиҗәле файдаланып, югары тизлекле тапшыру мөмкинлеген бирә.

Бүгенге көндә төп алым - 2,5D интеграциясе: берничә матрицаны интерпозерга янәшә урнаштыру. Киләсе адым - 3D интеграциясе, ул матрицаларны вертикаль рәвештә кремний аша үтүче виаслар (TSV) ярдәмендә өя, бу исә тыгызлыкны тагын да арттыра.

Модульле чип дизайнын (функцияләрне һәм схема төрләрен аеру) 3D стекинг белән берләштерү тизрәк, кечерәк һәм энергияне экономияләүче ярымүткәргечләр бирә. Хәтерне һәм исәпләүне бергә урнаштыру зур мәгълүмат җыелмаларына зур полоса киңлеге бирә - ясалма интеллект һәм башка югары җитештерүчән эш йөкләмәләре өчен идеаль.

Ләкин вертикаль катлауландыру кыенлыклар тудыра. Җылылык җиңелрәк җыела, бу җылылык белән идарә итүне һәм чыгаруны катлауландыра. Моны хәл итү өчен, тикшеренүчеләр җылылык чикләүләрен яхшырак хәл итү өчен яңа төргәкләү ысулларын алга сөрәләр. Шулай да, импульс көчле: чиплетларның конвергенциясе һәм 3D интеграциясе киң таралган җимергеч парадигма буларак карала - Мур законы тәмамланган урында факелны күтәрергә әзер.

Бастырып чыгару вакыты: 2025 елның 15 октябре